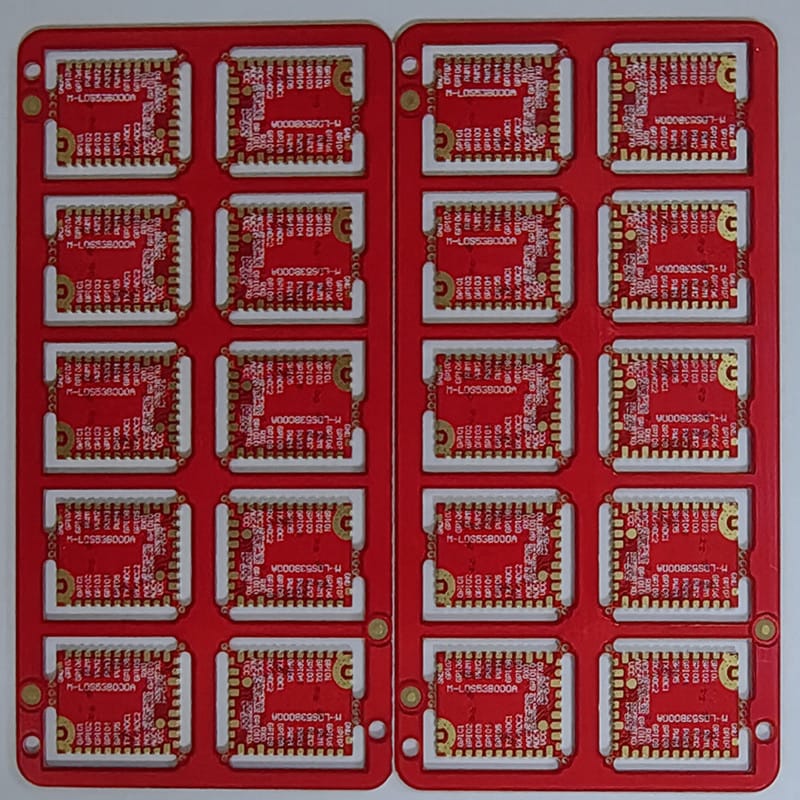

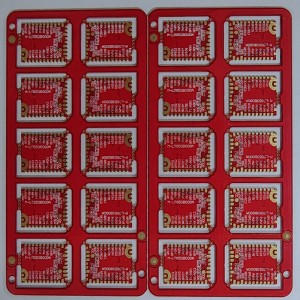

Prototyp-Leiterplatten ROTE Lötmaske mit Zinnenlöchern

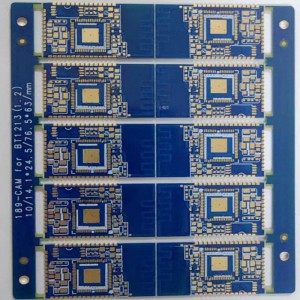

Produktspezifikation:

| Grundmaterial: | FR4 TG140 |

| PCB-Dicke: | 1,0 +/-10 % mm |

| Anzahl der Schichten: | 4L |

| Kupferdicke: | 1/1/1/1 Unze |

| Oberflächenbehandlung: | ENIG 2U“ |

| Lötstoppmaske: | Glänzend rot |

| Siebdruck: | Weiß |

| Spezialverfahren: | Pth halbe Löcher an den Kanten |

Anwendung

Die Verfahren zum plattierten Halblochverfahren sind:

1. Bearbeiten Sie das halbseitige Loch mit einem doppelten V-förmigen Schneidwerkzeug.

2. Der zweite Bohrer fügt Führungslöcher an der Seite des Lochs hinzu, entfernt die Kupferhaut im Voraus, reduziert Grate und verwendet Nutfräser anstelle von Bohrern, um die Geschwindigkeit und die Fallgeschwindigkeit zu optimieren.

3. Tauchen Sie Kupfer ein, um das Substrat zu galvanisieren, sodass eine Kupferschicht auf die Lochwand des runden Lochs am Rand der Platine galvanisiert wird.

4. Herstellung der Außenschichtschaltung. Nach der Laminierung, Belichtung und Entwicklung des Substrats in dieser Reihenfolge wird das Substrat einer sekundären Kupfer- und Zinnbeschichtung unterzogen, sodass die Kupferschicht an der Lochwand des runden Lochs am Rand der Platine dicker wird und die Kupferschicht zum Schutz vor Korrosion mit einer Zinnschicht bedeckt wird.

5. Halblochformung: Schneiden Sie das runde Loch an der Kante des Bretts in zwei Hälften, um ein Halbloch zu formen.

6. Im Schritt des Entfernens der Folie wird die während des Folienpressvorgangs gepresste Antigalvanisierungsfolie entfernt;

7. Ätzen: Das Substrat wird geätzt und das freiliegende Kupfer auf der äußeren Schicht des Substrats wird durch Ätzen entfernt.

8. Zinnstripping: Das Substrat wird von Zinn befreit, so dass das Zinn auf der Halblochwand entfernt werden kann und die Kupferschicht auf der Halblochwand freigelegt wird.

9. Nach dem Formen die Einheitsplatten mit rotem Klebeband zusammenkleben und die Grate durch die alkalische Ätzlinie entfernen

10. Nach der zweiten Verkupferung und Verzinnung des Substrats wird das runde Loch am Rand der Platte in zwei Hälften geschnitten, um ein halbes Loch zu bilden, da die Kupferschicht der Lochwand mit einer Zinnschicht bedeckt ist und die Kupferschicht der Lochwand vollständig mit der Kupferschicht der äußeren Schicht des Substrats verbunden ist. Durch die starke Bindungskraft kann wirksam verhindert werden, dass die Kupferschicht an der Lochwand beim Schneiden abgezogen wird oder sich das Kupfer verzieht.

11. Nachdem die Halblochbildung abgeschlossen ist, wird der Film entfernt und anschließend geätzt, sodass die Kupferoberfläche nicht oxidiert, wodurch das Auftreten von Kupferrückständen oder sogar Kurzschlüssen wirksam vermieden und die Ausbeute der metallisierten Halbloch-PCB-Leiterplatte verbessert wird.

FAQs

Bei der plattierten Halbbohrung oder Zinnenbohrung handelt es sich um eine stempelförmige Kante, die durch Halbieren der Kontur entsteht. Die plattierte Halbbohrung ist eine höherwertige plattierte Kante für Leiterplatten, die üblicherweise für Platinenverbindungen verwendet wird.

Vias dienen als Verbindung zwischen Kupferschichten auf einer Leiterplatte, während PTHs in der Regel größer als Vias sind und als plattierte Löcher für die Aufnahme von Bauteilanschlüssen dienen – wie z. B. nicht-SMT-Widerständen, Kondensatoren und DIP-Gehäuse-ICs. PTHs können auch als Löcher für mechanische Verbindungen verwendet werden, Vias hingegen nicht.

Die Beschichtung der Durchgangslöcher besteht aus Kupfer, einem Leiter, der die elektrische Leitfähigkeit durch die Platine gewährleistet. Nicht beschichtete Durchgangslöcher sind nicht leitfähig. Wenn Sie diese verwenden, können Sie also nur auf einer Seite der Platine nutzbare Kupferbahnen haben.

Es gibt drei Arten von Löchern in einer Leiterplatte: Durchkontaktierte Löcher (Plated Through Hole, PTH), nicht durchkontaktierte Löcher (Non-Plated Through Hole, NPTH) und Via Holes. Diese dürfen nicht mit Schlitzen oder Ausschnitten verwechselt werden.

Gemäß IPC-Standard beträgt er +/-0,08 mm für pth und +/-0,05 mm für npth.